APPLICATION NOTE SOFTWARE

# UAC 357xB Programmer's Guide

# Contents

| Page | Section  | Title                                              |

|------|----------|----------------------------------------------------|

| 4    | 1.       | Introduction                                       |

| 5    | 2.       | V8 Firmware Source Files                           |

| 7    | 3.       | Bootloader Concept                                 |

| 7    | 3.1.     | External EEPROM                                    |

| 7    | 3.1.1.   | Introduction                                       |

| 7    | 3.1.2.   | EEPROM Types                                       |

| 8    | 3.1.3.   | EEPROM bootstrap options                           |

| 9    | 3.1.4.   | EEPROM content                                     |

| 9    | 3.1.4.1. | Header                                             |

| 10   | 3.1.5.   | EEPROM Configuration Section                       |

| 10   | 3.1.5.1. | I/O and HID                                        |

| 16   | 3.1.5.2. | The Section1 Concept – data_sec1.asm               |

| 17   | 3.1.6.   | External EEPROM                                    |

| 18   | 3.1.6.1. | Content of the external EEPROM                     |

| 19   | 3.1.7.   | The Plug-in Concept                                |

| 20   | 4.       | USB Descriptor                                     |

| 20   | 4.1.     | USB_DESCRIPTOR.ASM                                 |

| 20   | 4.1.1.   | Device Descriptor (Chapter 9.6.1)                  |

| 20   | 4.1.2.   | Configuration Descriptor (Chapter 9.6.2)           |

| 20   | 4.1.3.   | Interface Descriptors (Chapter 9.6.3)              |

| 23   | 5.       | Handling of Class Specific Requests                |

| 23   | 5.1.     | Introduction                                       |

| 23   | 5.2.     | Audio-Control Handling                             |

| 25   | 5.2.1.   | GET-Requests and SET-Requests.                     |

| 29   | 5.2.2.   | Examples                                           |

| 29   | 5.2.2.1. | How to add new Features and Requests               |

| 33   | 5.3.     | DSP Control                                        |

| 35   | 5.4.     | Sample Rate Control                                |

| 38   | 6.       | GPIO Handling                                      |

| 40   | 6.1.     | Memory Mapped Mode                                 |

| 40   | 6.2.     | Debouncing                                         |

| 41   | 6.3.     | Reporting the Keycode                              |

| 41   | 6.4.     | Toggle Keys                                        |

| 42   | 6.5.     | GPIO port configurations.                          |

| 43   | 6.6.     | The parallel interface mechanism (RD/STRB)         |

| 44   | 7.       | Alternate Downstream ISO Endpoint                  |

| 44   | 7.1.     | How to use the alternative downstream ISO-Endpoint |

## Contents, continued

| Page | Section | Title                                       |

|------|---------|---------------------------------------------|

| 45   | 8.      | Appendex 1: SDK                             |

| 46   | 9.      | Appendix 2: DSP Firmware                    |

| 46   | 9.1.    | Overview                                    |

| 47   | 9.2.    | User Registers                              |

| 57   | 10.     | Appendix 3: V8 Controller Registers         |

| 57   | 10.1.   | Overview                                    |

| 58   | 10.2.   | V8 Memory Layout                            |

| 59   | 10.3.   | V8 Peripherals & Control & Status Registers |

| 59   | 10.3.1. | V8 General & Interface Registers            |

| 64   | 10.4.   | USB Serial Engine Interface                 |

| 66   | 10.5.   | General Purpose IO Registers / Test Bus IF  |

| 67   | 10.6.   | Application specific registers              |

| 73   | 10.7.   | DSP EMU-control registers                   |

| 75   | 11.     | Glossary                                    |

| 76   | 12.     | Application Note History                    |

## **Programmer's Guide**

### 1. Introduction

The basic information on functionality and electrical characteristics is given in the data sheet UAC 357xB. This is based on the Micronas standard firmware or SDK firmware, which is a good example for a feature set needed in a general purpose USB audio codec.

The flexibility of the device, however, allows customization to match a specific application exactly. This is achieved by the use of a programmable internal microcontroller and supply of a software development kit (SDK).

The purpose of this paper is to provide all information which is needed to customize the UAC357xy firmware.

Beginning with general information on the SDK environment and usage, an explanation of the standard firmware structure is given. This is followed by the detailed description of all functions which may be modified on customization, like default values, descriptors and all audio class related items. This tutorial is completed with register lists for both V8-microcontroller and DSP.

Information on the USB chapter 9 handling is not given because this routines are strictly tied to the hardware of the chip and it is not recommended to modify this blocks. It is also not possible to modify the DSP firmware.

# 2. V8 Firmware Source Files

The Micronas-Standard-Firmware package consists of the following files:

# Table 2–1: Source Files

| File Name              | Description                                  |  |  |

|------------------------|----------------------------------------------|--|--|

| data_fixed_ram.asm     | RAM variables with fixed address             |  |  |

| data_sec1.asm          | Section1 variables                           |  |  |

| dsp_control.asm        | controls the audio func-<br>tions in the DSP |  |  |

| emu_flash.asm          | structure for the I2C-<br>EEPROM             |  |  |

| gpio_control.asm       | GPIO communicaton and the HID                |  |  |

| i2c_drv.asm            | I2C driver                                   |  |  |

| iso_down_as1.asm       | alternate setting 1 for<br>downstream        |  |  |

| iso_down_as2.asm       | alternate setting 2 for<br>downstream        |  |  |

| iso_down_as3.asm       | alternate setting 3 for<br>downstream        |  |  |

| iso_up_as1.asm         | alternate setting 1 for<br>upstream          |  |  |

| iso_up_as2.asm         | alternate setting 2 for<br>upstream          |  |  |

| iso_up_as3.asm         | alternate setting 3 for<br>upstream          |  |  |

| macros.asm v8 macros   |                                              |  |  |

| main.asm               | main program – includes<br>all other .asm`s  |  |  |

| main_config.asm        | memory map of the V8<br>address space        |  |  |

| main_include.asm       | wakeup routines, initialisa-<br>tions        |  |  |

| main_upper_rom.asm     | content of upper rom space                   |  |  |

| timer_drv.asm          | Timer driver                                 |  |  |

| usb_appl_interface.asm | application specific chap-<br>ter 9 stuff    |  |  |

| usb_audio_ctl.asm      | handles audio class<br>requests              |  |  |

# Table 2–1: Source Files

| File Name                     | Description                                   |

|-------------------------------|-----------------------------------------------|

| usb_audio_ctl_include.as<br>m | routines and tables for audio class requests  |

| usb_ch9.asm                   | application independant<br>chapter 9 handling |

| usb_class.asm                 | branch handler to class spec. requests        |

| usb_descriptor_xp.asm         | Standard Descriptor<br>("WINXP-proved")       |

| usb_hid_ctl.asm               | empty – handles hid class<br>requests         |

| usb_vend_class.asm            | empty – handles vendor<br>class requests      |

| usb_vendor.asm                | handles vendor spec chap-<br>ter 9 requests   |

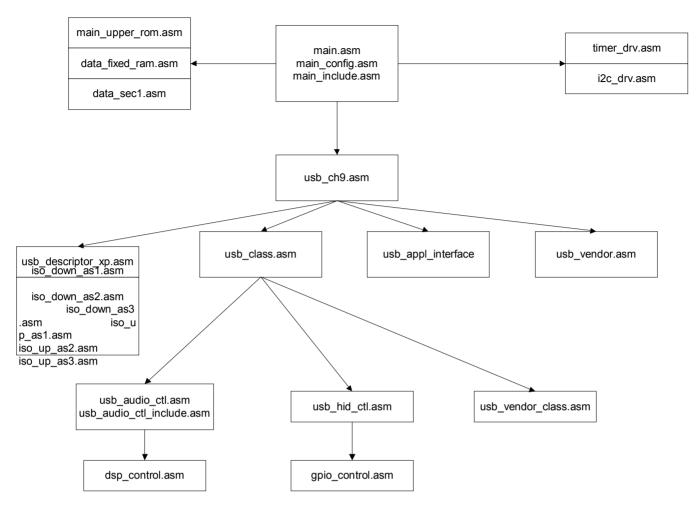

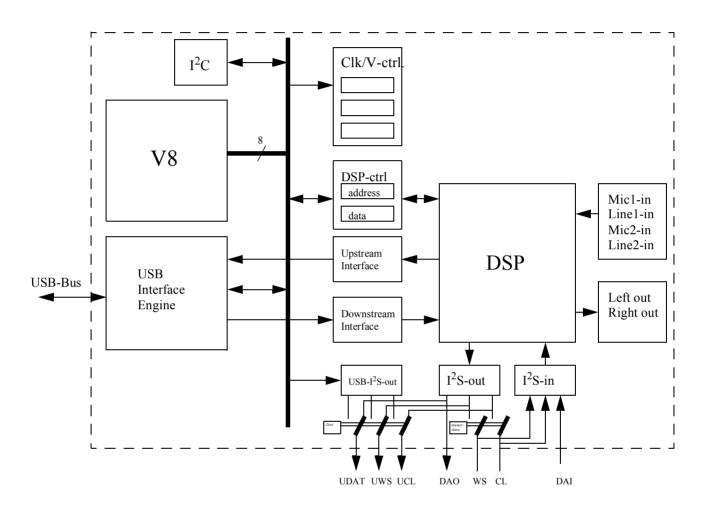

The following diagram displays how all these files are related to each other:

**Fig. 2–1:** Firmware overview

#### 3. Bootloader Concept

-> von W. Platzer bis KW 25

### **3.1. External EEPROM**

#### 3.1.1. Introduction

The UAC 357xB can load its configuration and plug-ins out of an external  $I^2C$  EEPROM.

#### 3.1.2. EEPROM Types

The UAC 357xB can have different EEPROMS connected to the I<sup>2</sup>C bus. The UAC 357xB is working as an I<sup>2</sup>C bus master at this point in time. Depending on EEPROM size the EEPROM can hold different content (see Table 3–1)

# Table 3–1: Supported I<sup>2</sup>C EEPROM types

| EEPROM size | Purpose                                                         |

|-------------|-----------------------------------------------------------------|

| 2kbit       | Configuration only                                              |

| 4-32kbit    | Configuration<br>Plug-in software                               |

| 64kbit      | Configuration<br>On reset loadable firmware                     |

| 128kbit     | Configuration<br>On reset loadable firmware<br>Plug-in software |

## **3.1.3. EEPROM bootstrap options**

The EEPROM configuration can be set with bootstrap options at the pins USBDAT, USBCLK and USBWSO (see Table 3–2).

# Table 3–2:

| USBWSO | USBDAT | USBCLK     | Address<br>Subaddress       | Purpose                                                                                         |

|--------|--------|------------|-----------------------------|-------------------------------------------------------------------------------------------------|

| 1      | 1      | don't care |                             | internal ROM only I <sup>2</sup> C master disabled                                              |

| 1      | 0      | don't care | 0x50<br>1byte subaddressing | Configuration data<br>Plug-in Software<br>100kHz I <sup>2</sup> C master                        |

| 0      | 1      | 0          | 0x51<br>2byte subaddressing | Configuration data<br>On reset loadable firmware<br>Plug-in software<br>400kHz I <sup>2</sup> C |

| 0      | 1      | 1          | 0x52<br>2byte subaddressing | Configuration data<br>On reset loadable firmware<br>Plug-in software<br>400kHz I <sup>2</sup> C |

| 0      | 0      | 0          | 0x51<br>2byte subaddressing | Configuration data<br>On reset loadable firmware<br>Plug-in software<br>100kHz I <sup>2</sup> C |

| 0      | 0      | 1          | 0x52<br>2byte subaddressing | Configuration data<br>On reset loadable firmware<br>Plug-in software<br>100kHz I <sup>2</sup> C |

### 3.1.4. EEPROM content

## 3.1.4.1. Header

The first byte in the serial EEPROM describes the EEPROM content (see Table 3–3).

Table 3–3: EEPROM configuration byte

| bit function        |                        |

|---------------------|------------------------|

| bit[7]              | verify checksum        |

| bit[36]             | must be set to 0x00    |

| bit[2] new firmware |                        |

| bit[1]              | plug-in                |

| bit[0]              | UAC357xB configuration |

This allows to have 3 different sections in the EEPROM. The address and length of all this sections are stored in the following locations in the EEPROM.

# 3.1.5. EEPROM Configuration Section

| Address         | Function                                              |

|-----------------|-------------------------------------------------------|

| 0x0000          | EEPROM configuration                                  |

| 0x0001 / 0x0002 | Configuration section length<br>High Byte / Low Byte  |

| 0x0003 / 0x0004 | Configuration section address<br>High Byte / Low Byte |

| 0x0005 / 0x0006 | Plug-in section length<br>High Byte / Low Byte        |

| 0x0007 / 0x0008 | Plug-in section address<br>High Byte / Low Byte       |

| 0x0009 / 0x000A | Firmware section length<br>High Byte / Low Byte       |

| 0x000B / 0x000C | Firmware section address<br>High Byte / Low Byte      |

# 3.1.5.1. I/O and HID

| Address | Function                                                                                | Name           |

|---------|-----------------------------------------------------------------------------------------|----------------|

| 0x00    | MIN_PB_VOLUME                                                                           | MIN_PB_VOLUME  |

|         | bit [70] volume of the DAC output after configuration:<br>0x00 0dB<br>0xEC -20dB        |                |

|         | gets overwritten by Set_Volume requests later on                                        |                |

| 0x01    | reserved 2                                                                              | Reserved_2     |

|         | bit [70] reserved must be set to 0x00                                                   |                |

| 0x02    | V8_CTL_DEFAULT                                                                          | V8_CTL_DEFAULT |

|         | bit [7]set to 0 for GPIO[11] standard output<br>set to 1 for GPIO[11] enable PWM output |                |

|         | bit [60] reserved must be set to 0x08                                                   |                |

| 0x03    | reserved 3                                                                              | Reserved_3     |

|         | bit [70] reserved must be set to 0x01                                                   |                |

| 0x04    | reserved 4                                                                              | Reserved_4     |

|         | bit [70] reserved must be set to 0x09                                                   |                |

| Address | Function              |                                                                                                                        | Name          |

|---------|-----------------------|------------------------------------------------------------------------------------------------------------------------|---------------|

| 0x05    | reserved 5            |                                                                                                                        | Reserved_5    |

|         | bit [70]              | reserved must be set to 0x05                                                                                           |               |

| 0x06    | reserved 6            |                                                                                                                        | Reserved_6    |

|         | bit [70]              | reserved must be set to 0x0b                                                                                           |               |

| 0x07    | reserved 7            |                                                                                                                        | Reserved 7    |

|         | bit [70]              | reserved must be set to 0x04                                                                                           | _             |

| 0x08    | Miscellaneo           | us configuration 1                                                                                                     | Config_Misc_1 |

|         | bit [7]               | 0: μC uses USBWSO, USBDAT, USBCLK interface<br>1: DSP I <sup>2</sup> S out uses USBWSO, USBDAT, USBCLK interface       | <u> </u>      |

|         | bit [62]              | reserved must be set to MSB 01000 LSB                                                                                  |               |

|         | bit [10]              | selects audio oversampling clock frequency pin MCLK<br>00: 36.8MHz<br>01: 24.576MHz<br>10: 18.432MHz<br>11: do not use |               |

| 0x09    | Analog Con            | trol                                                                                                                   | ANCTR         |

|         | bit[7]                | outlron :<br>0 : disable headphone opamp<br>1 : enable headphone opamp, force sref to on state (default)               |               |

|         | bit[6]                | srefon :<br>0 : sref off<br>1 : sref on (default)                                                                      |               |

|         | bit[5]                | filton :<br>0 : disable filter opamp<br>1 : enable filter opamp                                                        |               |

|         | bit[4]                | reserved, must be set to zero                                                                                          |               |

|         | bit[3]                | Internal reset enable                                                                                                  |               |

|         | bit[2]                | Pseudo differential output mode                                                                                        |               |

|         | bit[1]                | Common output mode                                                                                                     |               |

|         | bit[0]                | setagn : set voltage of sref<br>0 : 1.725V<br>1 : 2.3V                                                                 |               |

| 0x0a    | GPIO[70]              | direction                                                                                                              | PIO           |

|         | 0: input<br>1: output |                                                                                                                        |               |

|         | bit [70]              | set GPIO [70] to input/output                                                                                          |               |

| 0x0b    | GPIO[118]             | direction                                                                                                              | PIO2          |

|         | bit [74]              | reserved must be set to MSB 0000 LSB                                                                                   |               |

|         | 0: input<br>1: output |                                                                                                                        |               |

|         | bit [30]              | set GPIO [118] to input/output                                                                                         |               |

# UAC 357xB

| Address | Function                                    |                                                            | Name        |

|---------|---------------------------------------------|------------------------------------------------------------|-------------|

| 0x0c    | GPIO[70]                                    | pulldown enable                                            | PDEN        |

|         | 0: disable pull-down<br>1: enable pull-down |                                                            |             |

|         | bit [70]                                    | GPIO [70] pull-down resistor enable / disable              |             |

| 0x0d    | GPIO[118                                    | 3] pull-down enable                                        | PDEN2       |

|         | bit [74]                                    | reserved must be set to MSB 0000 LSB                       |             |

|         | 0: disable p<br>1: enable pu                |                                                            |             |

|         | bit [30]                                    | GPIO [118] pull-down resistor enable / disable             |             |

| 0x0e    | GPIO[70]                                    | driver strength                                            | PS          |

|         | 0: weak<br>1: strong                        |                                                            |             |

|         | bit [70]                                    | GPIO [70] driver strength weak / strong                    |             |

| 0x0f    | GPIO[118                                    | 3] driver strength                                         | PS2         |

|         | 0: weak<br>1: strong                        |                                                            |             |

|         | bit [7]                                     | Pins: DAO, DAI, WSI, CLI driver strength weak / strong     |             |

|         | bit [6]                                     | Pins: USBWSO, USBCLK, USBDAT driver strength weak / strong |             |

|         | bit [5] Pins:<br>strong                     | SOF, SEN, SUSPENDQ, TRDY driver strength weak /            |             |

|         | bit [4]                                     | Pins: STRB, RD DRIVER STRENGTH weak / strong               |             |

|         | bit [30]                                    | GPIO [118] driver strength weak / strong                   |             |

| 0x10    | IO Config                                   | 1                                                          | IO_CONFIG_1 |

|         | 0 : input / tr<br>1 : output                | istate                                                     |             |

|         | bit [7]                                     | Direction of pin: STRB                                     |             |

|         | bit [6]                                     | Direction of pin: RD                                       |             |

|         | bit [5]                                     | Direction of pin: USBDAT                                   |             |

|         | bit [4]                                     | Direction of pin: USBCLK                                   |             |

|         | bit [3]                                     | reserved set to 0:                                         |             |

|         | bit [2]                                     | Direction of pin: CLI                                      |             |

|         | bit [1]                                     | Direction of pin: WSI                                      |             |

|         | bit [0]                                     | Direction of pin: DAI                                      |             |

| Address        | Function                                                                                                        | Name         |

|----------------|-----------------------------------------------------------------------------------------------------------------|--------------|

| 0x11           | IO Config 2                                                                                                     | IO_CONFIG_2  |

|                | 0 : input / tristate<br>1 : output                                                                              |              |

|                | bit [7] Direction of pin: MCLK                                                                                  |              |

|                | bit [6] Direction of pin: DAO                                                                                   |              |

|                | bit [5] Direction of pin: USBWS                                                                                 |              |

|                | bit [4] Direction of pin: SEN                                                                                   |              |

|                | 0: disable pull-down resistor<br>1: enable pull-down resistor                                                   |              |

|                | bit [3] enable pull-down resistor of pin VBUS:                                                                  |              |

|                | 0 : input / tristate<br>1 : output                                                                              |              |

|                | bit [2] Direction of pin: TRDY                                                                                  |              |

|                | bit [1] Direction of pin: SOF                                                                                   |              |

|                | bit [0] Direction of pin: SUSPENDQ                                                                              |              |

| 0x12           | reserved 8                                                                                                      | reserved_8   |

|                | bit [7:0] reserved set to 0xa7                                                                                  |              |

| 0x13           | reserved 9                                                                                                      | reserved_9   |

|                | bit [7:0] reserved set to 0x91                                                                                  |              |

| 0x14           | Key timer                                                                                                       | reserved_8   |

|                | Timer value for debouncing of the HID keys                                                                      |              |

|                | bit [7:0] set to a value between 0x01 and 0xff; default 0x7f                                                    |              |

| 0x15 -         | equalizer coefficients                                                                                          |              |

| 0x44           | coefficients for the 5-band parametric equalizer                                                                |              |

| 0x45 -         | I <sup>2</sup> S configuration                                                                                  | i2S_CONFIG   |

| 0x47           | for a detailed description see register description of the DSP                                                  |              |

| 0x48 -<br>0x49 | I <sup>2</sup> S record selection                                                                               | i2S_CONFIG   |

| 0X49           | for a detailed description see register description of the DSP                                                  |              |

| 0x4A -<br>0x50 | Bass Boost On Setting<br>Micronas Bass settings for Bass Boost On                                               | BassBoostOn  |

|                | for a detailed description see Micronas Bass for UAC357xB Application note                                      |              |

| 0x51 -<br>0x57 | Bass Boost Off Setting<br>Micronas Bass settings for Bass Boost On                                              | BassBoostOff |

|                | for a detailed description see Micronas Bass for UAC357xB Application note                                      |              |

| 0x58           | AGC decay                                                                                                       | AgcDecay     |

|                | sets the AGC decay time for the DAC path. For more information see the the regis-<br>ter description of the DSP |              |

| 0x59           | DSP mode selection                                                                                              | DspMode      |

|                | selects the required mode for the DSP. Full feature mode(72MHz) or reduced feature mode(48Mhz).                 |              |

|                | 0: Full feature mode(72MHz)<br>1: Reduced feature mode(48MHz                                                    |              |

# UAC 357xB

| Address | Function                                                                                         | Name           |

|---------|--------------------------------------------------------------------------------------------------|----------------|

| 0x5a    | DAC on/off                                                                                       | AgcDecay       |

|         | Turns the required bit [7:2]reserved should be set to 0                                          |                |

|         | bit [1] reserved                                                                                 |                |

|         | bit [0] 0: Stereo DAC Off<br>1: Stereo DAC On                                                    |                |

| 0x5b    | reserved 10                                                                                      | reserved_10    |

|         | reserved set to 0x00                                                                             |                |

| 0x5c -  | Vendor ID                                                                                        | VendorId       |

| 0x5d    | the USB vendor ID. e.g. Micronas has 0x074d                                                      |                |

|         | byte order low-byte / high-byte                                                                  |                |

| 0x5e -  | Product ID                                                                                       | ProductId      |

| 0x5f    | the USB product ID. e.g. UAC3576B has 0x3576                                                     |                |

|         | byte order low-byte / high-byte                                                                  |                |

| 0x60 -  | Device release code                                                                              | bcdDevice      |

| 0x61    | <b>BCD number!!</b> : use only binary coded decimals here. Using hex numbers will confuse hosts. |                |

|         | order low-byte / high-byte                                                                       |                |

| 0x62    | iManufacture                                                                                     | iManufacture   |

|         | index number of the manufacture string in the EEPROM. valid numbers 03                           |                |

|         | 0: no string in the table                                                                        |                |

|         | 1,2,3: string number in the table                                                                |                |

| 0x63    | iProduct                                                                                         | iProduct       |

|         | index number of the product string in the EEPROM. valid numbers 03                               |                |

|         | 0: no string in the table                                                                        |                |

|         | 1,2,3: string number in the table                                                                |                |

| 0x64    | iSerialNumber                                                                                    | iserial number |

|         | index number of the serial number string in the EEPROM. valid numbers 03                         |                |

|         | 0: no string in the table                                                                        |                |

|         | 1,2,3: string number in the table                                                                |                |

| 0x65    | iConfig                                                                                          | iConfig        |

|         | index number of the configuration string in the EEPROM. valid numbers 03                         |                |

|         | 0: no string in the table                                                                        |                |

|         | 1,2,3: string number in the table                                                                |                |

| 0x66    | bmAttributes                                                                                     | bmAttributes   |

|         | reserved set to 0x00                                                                             |                |

| 0x67    | Max power                                                                                        | MaxPower       |

|         | reserved set to 0x00                                                                             |                |

| 0x68    | Interval                                                                                         | bInterval      |

|         | reserved set to 0x00                                                                             |                |

| Address | Function                                             | Name     |

|---------|------------------------------------------------------|----------|

| 0x69 -  | Pointer string 0                                     | pString0 |

| 0x6a    | value: 0xa771                                        |          |

| 0x6b -  | Pointer string 1                                     | pString1 |

| 0x6c    | value: 0xa775                                        |          |

| 0x6d -  | Pointer string 2                                     | pString2 |

| 0x6e    | value: pString1 + *pString1                          |          |

| 0x6f -  | Pointer string 3                                     | pString3 |

| 0x70    | value: pString1 + *pString1 + *pString2              |          |

| 0x71 -  | String 0                                             | String0  |

| 0x74    | byte 0: 0x04                                         |          |

|         | byte 1: 0x03                                         |          |

|         | byte 1: 0x09                                         |          |

|         | byte 1: 0x04                                         |          |

| 0x75 -  | Strings 13                                           | String1  |

| 0xXX    | all strings are currently ASCII. No Unicode support. | String2  |

|         | String format:                                       | String3  |

|         | byte 0: length of ASCII string + 2                   |          |

|         | byte 1: 0x03                                         |          |

|         | byte 2n ASCII string                                 |          |

#### 3.1.5.2. The Section1 Concept – data\_sec1.asm

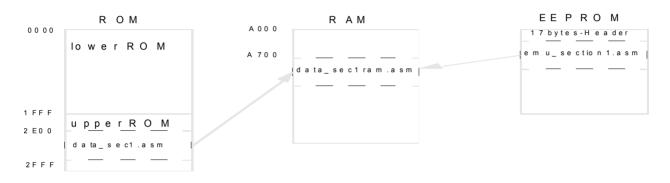

The Section1 is the first section of an optionally attached external EEPROM and is used to hold all variables and default values that may be different from one application to the other, based on the same internal ROM-firmware. The standard firmware handles 256-bytes Section1 data.

All data are defined in data\_sec1.asm. All data names here have the prefix ",SED\_DEFAULT\_ ",

(originally an sed-script was used to handle this file).

This file is included at the position 0x2E00 of the upper-ROM and is the default Section1 of a ROM firmware. The assembler script generates the file "data\_sec1ram.asm" which is an mirror image of the Section1 in the RAM area at 0xA700 by just inserting placeholders using the same names apart from the SED\_DEAULT prefix. The scripts also generates the file "emu\_section1.asm" which is a hex-representation of the data\_sec1.asm. This file is then included in the "emu\_flash.asm". This serves as the default Section1 code in the external EEPROM. So without changing ROM firmware the default setting and the descriptor IDs and strings can be modified.

Note: It is not allowed to change the length or the ordering of the Section1 data in the EEPROM. Length and ordering must be identical with that of the upper ROM Section1. Descriptor strings are not affected by the length-restriction as long as the 256-byte limit is not violated.

#### Fig. 3–1:

**Note:** The bootloader (see "The Bootloader Concept") loads the data\_sec1.asm from the upper ROM into the placeholder-RAM area and overwrites this area with Section1 - data coming from the external EEPROM (if an EEPROM with Section1 data is connected.

The Section1 concept is targeted for a device without shadow RAM. Applications based on devices with Shadow RAM can keep all Section1 data as part of the emulatable lower ROM, of course.

#### **3.1.6. External EEPROM**

The UAC 357xB is equipped with it's own ROM including the Micronas firmware necessary for operation.

Optionally, the IC can be operated with the followings oft ware configurations:

- 1. Micronas firmware (internal ROM)

- 2. customer-specific firmware (external EEPROM)

- 3. Micronas firmware plus customer-specific plug-in code

- 4. Structure of the external EEPROM

The bootloader handles an external  $I^2C$ -EEPROM with automatic detection of presence and structure and download of code and data from up to four sections.

The header byte tells the bootloader how the EEPROM is structured and the sections are used as follows:

#### Table 3–5: Header Byte

| Bit 7              | Bit 6 | Bit 5 | Bit 4 | Bit 3      | Bit 2      | Bit 1      | Bit 0      |

|--------------------|-------|-------|-------|------------|------------|------------|------------|

| 1=test<br>checksum | 0     | 0     | 0     | 1=Section4 | 1=Section3 | 1=Section2 | 1=Section1 |

Section1: default data and programmable descriptor components (see The Section1 Concept)

Section2: used for plug-ins; small pieces of code that extend a given ROM firmware

Section3: contains the V8 code for the Shadow RAM

Section4: contains the XDFP code; the bootloader loads it into the external DSP Emu-RAM

## 3.1.6.1. Content of the external EEPROM

# Table 3–6:

| Addr. | Content                                                  | Byte        |  |  |

|-------|----------------------------------------------------------|-------------|--|--|

| 0x00  | length in bytes of Section1 + 1 for checksum             | High Byte   |  |  |

| 0x01  | length in bytes of Section1 + 1 for checksum             | Low Byte    |  |  |

| 0x02  | address-offset in bytes of Section1 related to addr 0000 | High Byte   |  |  |

| 0x03  | length in bytes of Section2 + 1 for checksum             | High Byte   |  |  |

| 0x04  | length in bytes of Section2 + 1 for checksum             | Low Byte    |  |  |

| 0x05  | address-offset in bytes of Section2 related to addr 0000 | High Byte   |  |  |

| 0x06  | length in bytes of Section3 + 1 for checksum             | High Byte   |  |  |

| 0x07  | length in bytes of Section3 + 1 for checksum             | Low Byte    |  |  |

| 0x08  | address-offset in bytes of Section3 related to addr 0000 | High Byte   |  |  |

| 0x09  | length in bytes of Section4 + 1 for checksum             | High Byte   |  |  |

| 0x0A  | length in bytes of Section4 + 1 for checksum             | Low Byte    |  |  |

| 0x0B  | address-offset in bytes of Section4 related to addr 0000 | High Byte   |  |  |

| 0x0C  | address-offset in bytes of Section4 related to addr 0000 | Low Byte    |  |  |

| 0x0D  | DATA of Section1 + 1 for checksum                        | Header Byte |  |  |

| 0x0E  |                                                          |             |  |  |

| 0xxx  | DATA of Section2 + 1 for checksum                        | Header Byte |  |  |

| 0xxx  |                                                          |             |  |  |

| 0xxx  | DATA of Section3 + 1 for checksum                        | Header Byte |  |  |

| 0xxx  |                                                          |             |  |  |

| 0xxx  | DATA of Section4 + 1 for checksum                        | Header Byte |  |  |

| 0xxx  |                                                          |             |  |  |

The checksum is an XOR over all bytes of a section the address-offset of Section1 is 0x11 (17 Bytes Header)

# 3.1.7. The Plug-in Concept

### 4. USB Descriptor

#### 4.1. USB\_DESCRIPTOR.ASM

This part of the source code covers all information that is reported to the host upon enumeration. The "DESCRIP-TOR" provides a complete description of the USB-characteristic. It is assumed that the reader is familiar with the USB-basics and it is recommended to have the USB-SPEC 1.1 nearby because it is often referred to this paper. The following paragraphs explain the structure of the descriptor and the functionality of the Micronas Standard Descriptor.

The descriptor is split into the following parts:

- Device Descriptor

- Configuration Descriptor

- Interface Descriptors

#### 4.1.1. Device Descriptor (Chapter 9.6.1)

1 here is the place to provide formal information of the device like

- Manufacturer ID

- Product ID

- Release Numbers

- String Information

The Micronas Standard Descriptor keeps this kind of information EEPROM programmable (->FE-concept, ->Section1-concept). This, however, is important only when the device works with ROM-Firmware and taking only few programmable parts out of an external EEPROM.

### 4.1.2. Configuration Descriptor (Chapter 9.6.2)

Sometimes all but the device descriptor is called Configuration Descriptor but the exact definition is given in chapter 9.6.2 of the spec. The important points here are:

- number of interfaces (Chapter 9.6.3, note: wrong number here crashes all operating systems!)

- Attributes defines self/bus-powered and remote wakeup capability

- Maxpower in mA this must be set in case of bus-powered mode

The attributes and the maxpower are programmable via Section1.

The Micronas Standard Firmware uses the configuration string for a time code information

It is string 3 (index=3), and the V8-assembler directive "...datetime" generates the timing information automatically. This allows an easy check of the FW-version.

#### 4.1.3. Interface Descriptors (Chapter 9.6.3)

All USB-functions require a USB interface. The Standard Descriptor has 4 interfaces. This is coded as follows:

- .equ bNumInterfaces4

- .equ ISO\_CONTROL\_IFC\_NR0

- .equ ISO\_DOWN\_IFC\_NR1

- .equ ISO\_UP\_IFC\_NR2

- .equ HID\_IFC\_NR3

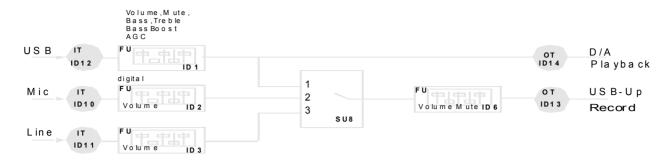

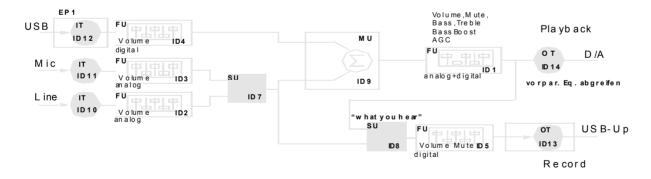

The **ISO\_CONTROL\_IFC** is a class specific descriptor and describes the path of the up- and downstream audio signal to and from the DSP. Here we define whether the device is an USB-Speaker, USB-Headset, or a USB soundcard for example. We also define here, how the device appears in the Windows mixer, for example if we have line-input or mic input or both. The rules for defining this structures can be found in the "Universal Serial Bus Device Class Definition for Audio Devices".

**Note:** The USB-Spec allows free combinations of input units, feature units, selector units, mixer unit, output units etc. A first serious restriction here, however, is the Windows mixer, which must be observed, if the device shall be shipped without additional drivers. The WIN mixer is not flexible and requires a strict scheme of devices working on the recording mixer and devices working on the playback mixer. Also the choice of features is limited here. For example: we don't have mute buttons for the recordings devices, or how shall we switch on and off an AGC for the mic-input? No way.

Apart from that, the WIN-mixer shows different performance in different WIN-versions. The mixer WIN-ME is nearly unusable.

The second restriction is the limited capability of the operating system in parsing this part of the descriptor due to a bad implementation of the USB-Spec. This causes many bluescreens or system hang-ups and requires try & error methods, because nobody can give a reliable answer here on how the descriptor should look like. The Micronas Standard Descriptor was tested on all WIN – operating systems and on MAC 9.1.

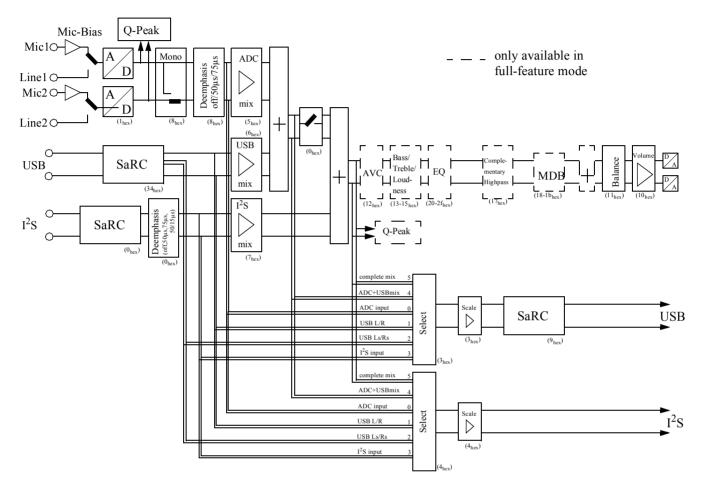

The **ISO\_CONTROL** interface reflects the following audio path in the Micronas Standard Descriptor.

Its the basic configuration of an USB codec. The additional (and already implemented) asynchronous I2S I/O features are not reflected here.

Other more complex structures are possible, but then the operating system eventually may not handle this and an additional vendor specific driver and mixer tool may be required.

The **ISO\_DOWN interface** covers the audio-downstream functionality. This interface has two alternate settings, describing the audio formats, which are supported by the chip. These are:

| Alternate Setting 1 | 16 bit mono   |  |  |

|---------------------|---------------|--|--|

| Alternate Setting 2 | 16 bit stereo |  |  |

The properties of each alternate setting are defined in the

CS-Audio Streaming Interface Format. Here it is declared that the chip handles continuos sampling rates. The range is defined with:

;ISO-SAMPLING RANGE

.equ LOW\_SAMPLE\_FREQ 6400

.equ HI\_SAMPLE\_FRE48000

This range is identical for all ISO-interfaces. The upper limit must never be exceeded.

Important also is the packet size which define the maximum bytes per frame. It is recommended to slightly exceed the theoretical value.

Example:16\_BIT\_STEREO at 48kHz require 48 x 2 x 2 = 192bytes

the value used in the descriptor is 200bytes

The following packet sizes should never be changed.

;PACKET SIZE

.equ 8\_BIT\_MONO 50 .equ 8\_BIT\_STEREO100 .equ 16\_BIT\_MONO100 .equ 16\_BIT\_STEREO200 .equ 24\_BIT\_MONO150 .equ 24\_BIT\_STEREO300

**Note:** The device is capable of handling 24bit downstream word also. But the standard descriptor does not declare this. The code for this (alternate setting 3), however, is provided.

The downstream uses endpoint 1.

The **ISO\_UP interface** covers the audio-upstream functionality. This interface has three alternate settings, describing the audio formats, which are supported by the chip. These are:

| Alternate Setting 1 | 08 bit mono   |  |  |

|---------------------|---------------|--|--|

| Alternate Setting 2 | 16 bit mono   |  |  |

| Alternate Setting 3 | 16 bit stereo |  |  |

The upstream uses endpoint 4 (coded as 84 - IN endpoint)

The HID interface contains the HID endpoint 3 (coded as 83 – IN endpoint) and the REPORT Descriptor. The Standard Descriptor assigns the following functions to the GPI-Ports:

| GPI 0 | Volume Up   |  |  |  |

|-------|-------------|--|--|--|

| GPI 2 | Volume Down |  |  |  |

| GPI 3 | Mute        |  |  |  |

| GPI 4 | Bass Boost  |  |  |  |

The key codes for GPIO5..7 are also reported to the host, but no HID-functions are assigned to this pins. This can be used in a vendor specific driver to trigger additional functions.

Important for the HID endpoint are:

- 0x0002;wMaxPacketSize

- .byte0xfe;bInterval

bInterval defines the polling interval in ms. This is a Section 1 variable (->FE-concept, ->Section1-concept).

**Note:** It is not recommended to change the MaxPacketSize in the HID-endpoint, because this requires deep familiarity with the TX-buffer handling.

More information on the HID handling can be found in the description of gpio\_control.asm.

#### 5. Handling of Class Specific Requests

#### 5.1. Introduction

The UACB needs class specific requests to handle the USB audio control. After an incoming request is identified as class specific further processing is done in the USB\_CLASS\_SETUP routine, located in usb\_class.asm.

Here first it is checked if its an audio class request. This happens in USB\_AUDIO\_CTL\_START in the file usb\_audio\_ctl.asm. If it is not identified here the same is tried with USB\_HID\_CTL\_START and USB\_VEND\_CLAS\_START but only audio-control and sample rate-control is supported in the standard firmware

# 5.2. Audio-Control Handling (usb\_audio\_ctl.asm, usb audio ctl include.asm, dsp control.asm)

It is recommended here to be familiar with the Universal Serial Bus Device CLass Definition for Audio Devices Specification, Release 1.0.

The number and kind of control request is strictly related to the **ISO\_CONTROL\_IFC** descriptor. That means if the descriptor is modified also the request handling needs to be modified (especially if new features are introduced). The standard firmware handles the following audio control requests for feature units (FU), selector units (SU) and mixer units (MU).

- FU1\_MUTE\_

- FU1\_VOL\_CH1

- FU1\_VOL\_CH2

- FU1\_BASS

- FU1\_TREBLE

- FU1\_AGC

- FU1\_BASSBOOST

- FU2\_MUTE

- FU2\_VOL

- FU3\_MUTE

- FU3\_VOL

- FU6\_MUTE

- FU6\_VOL

- SU7

- SU8

- MU9\_IN1

- MU9\_IN2

This was based on a descriptor which covered more functionality than the current descriptor.

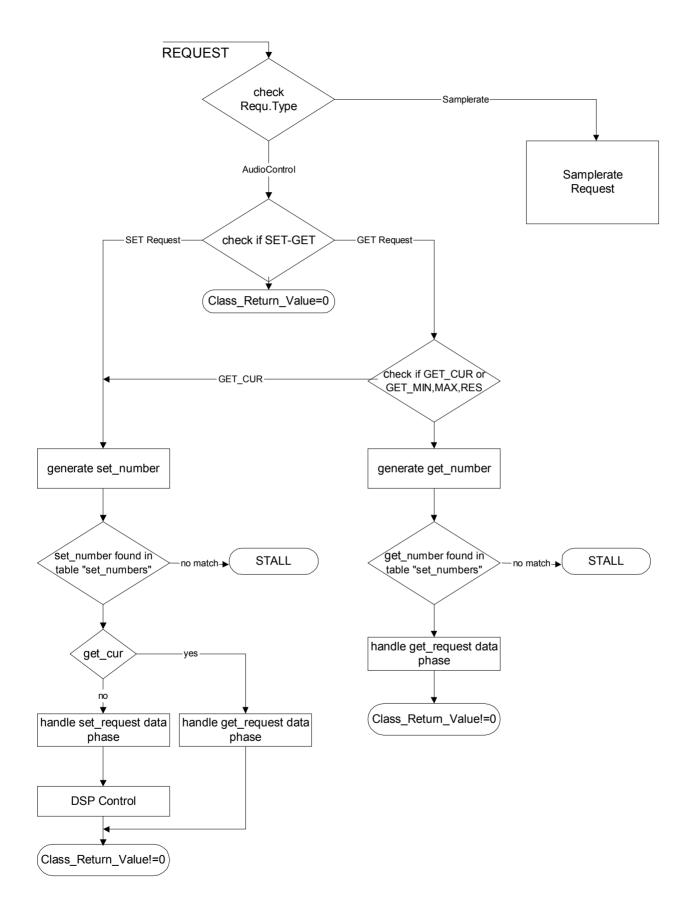

Fig. 5–1:

**Note:** Even this structure does not represent the complete audio structure of the device. All I2S functionality is not represented here and needs to be added in a future version.

**Fig. 5–2:** Audio request handling

#### 5.2.1. GET-Requests and SET-Requests.

The GET-requests are needed

1. to report the parameter range (MIN,MAX,RES) of the units to the host.

This information is located in ROM-table ROM\_USB\_MINMAXRES in usb audio ctl include.asm

ROM\_USB\_MINMAXRES:

| ROM_USB_VOL_MIN_FU1_CH1: | .rword 0xD700 |

|--------------------------|---------------|

| ROM_USB_VOL_MAX_FU1_CH1: | .rword 0x0000 |

| ROM_USB_VOL_RES_FU1_CH1: | .rword 0x0010 |

etc.

This, for example, tells the host that FU1 has an audio range from -40 dB to 0dB with a stepsize of 1dB.

# All parameters here are coded with 2-bytes even if only 1-byte is required. This simplifies programming

2. to report the current status (CUR) of the unit.

This information is located in RAM-table USB\_AUDIOCLASS\_SET\_CUR in usb\_audio\_ctl\_include.asm. The content of this table represents the current status of the audio parameters.

The CUR-parameters are not exactly identical with the values which are transmitted to the DSP.In some cases there must be a transformation first, to match the requirements of the DSP - algorithm. The SET requests are needed:

- 1. to set the CUR-parameters This request modifies the RAM-table USB\_AUDIOCLASS\_SET\_CUR and accordingly triggers the update of the DSP-parameters (dsp\_control.asm)

- 2. to set the sampling rate for the ISO upstream (endpoint control operation)

The method used for decoding the request types is table based. The idea behind this is:

The supported requests are represented by a certain number, which is calculated out of the requests components. These "magic numbers" are stored in the ROM-tables "set\_numbers" and "get\_numbers". Out of any incoming vendor request the same procedure is used to compute this number and then it is checked if this number is found in the set\_numbers or get\_numbers table. If the number is found, the corresponding table position represents the decoded request. If more requests needs to be decoded than provided in the standard firmware the procedure is needed to compute the "magic numbers". This is done with the help of Table 5–1 an Table 5–2.

| Request Nr. | wIndexH | wValueH | wValueL | magic number | Request Name      |

|-------------|---------|---------|---------|--------------|-------------------|

| 1           | 1       | 1       | 0       | 16           | FU1_MUTE_CUR      |

| 2           | 1       | 2       | 1       | 288          | FU1_VOL_CH1_CUR   |

| 3           | 1       | 2       | 2       | 544          | FU1_VOL_CH2_CUR   |

| 4           | 1       | 3       | 0       | 48           | FU1_BASS_CUR      |

| 5           | 1       | 5       | 0       | 80           | FU1_TREBLE_CUR    |

| 6           | 1       | 7       | 0       | 112          | FU1_AGC_CUR       |

| 7           | 1       | 9       | 0       | 144          | FU1_BASSBOOST_CUR |

| 8           | 2       | 1       | 0       | 17           | FU2_MUTE_CUR      |

| 9           | 2       | 2       | 0       | 33           | FU2_VOL_CUR       |

| 10          | 3       | 1       | 0       | 18           | FU3_MUTE_CUR      |

| 11          | 3       | 2       | 0       | 34           | FU3_VOL_CUR       |

| 12          | 6       | 1       | 0       | 21           | FU6_MUTE_CUR      |

| 13          | 6       | 2       | 0       | 37           | FU6_VOL_CUR       |

| 14          | 7       | 0       | 0       | 6            | SU7_CUR           |

| 15          | 8       | 0       | 0       | 7            | SU8_CUR           |

| 16          | 9       | 1       | 1       | 280          | MU9_IN1_CUR       |

| 17          | 9       | 2       | 1       | 296          | MU9_IN2_CUR       |

:

# Table 5–2: GET numbers

| Request Nr. | wIndexH | wValueH | wValueL | bRequest | magic number | Request Name           |

|-------------|---------|---------|---------|----------|--------------|------------------------|

| 1           | 1       | 2       | 1       | 82       | 288          | USB_VOL_MIN_FU1_CH1    |

| 2           | 1       | 2       | 1       | 83       | 1312         | USB_VOL_MAX_FU1_CH1    |

| 3           | 1       | 2       | 1       | 84       | 2336         | USB_VOL_RES_FU1_CH1    |

| 4           | 1       | 2       | 2       | 82       | 544          | USB_VOL_MIN_FU1_CH2    |

| 5           | 1       | 2       | 2       | 83       | 1568         | USB_VOL_MAX_FU1_CH2    |

| 6           | 1       | 2       | 2       | 84       | 2592         | USB_VOL_RES_FU1_CH2    |

| 7           | 1       | 3       | 0       | 82       | 48           | USB_BASS_MIN_FU1_CH0   |

| 8           | 1       | 3       | 0       | 83       | 1072         | USB_BASS_MAX_FU1_CH0   |

| 9           | 1       | 3       | 0       | 84       | 2096         | USB_BASS_RES_FU1_CH0   |

| 10          | 1       | 5       | 0       | 82       | 80           | USB_TREBLE_MIN_FU1_CH0 |

| 11          | 1       | 5       | 0       | 83       | 1104         | USB_TREBLE_MAX_FU1_CH0 |

| 12          | 1       | 5       | 0       | 84       | 2128         | USB_TREBLE_RES_FU1_CH0 |

| 13          | 2       | 2       | 0       | 82       | 33           | USB_VOL_MIN_FU02_CH0   |

| 14          | 2       | 2       | 0       | 83       | 1057         | USB_VOL_MAX_FU02_CH0   |

| 15          | 2       | 2       | 0       | 84       | 2081         | USB_VOL_RES_FU02_CH0   |

| 16          | 3       | 2       | 0       | 82       | 34           | USB_VOL_MIN_FU03_CH0   |

| 17          | 3       | 2       | 0       | 83       | 1058         | USB_VOL_MAX_FU03_CH0   |

| 18          | 3       | 2       | 0       | 84       | 2082         | USB_VOL_RES_FU03_CH0   |

| 19          | 6       | 2       | 0       | 82       | 37           | USB_VOL_MIN_FU06_CH0   |

| 20          | 6       | 2       | 0       | 83       | 1061         | USB_VOL_MAX_FU06_CH0   |

| 21          | 6       | 2       | 0       | 84       | 2085         | USB_VOL_RES_FU06_CH0   |

| 22          | 7       | 0       | 0       | 82       | 6            | USB_MIN_SU07           |

| 23          | 7       | 0       | 0       | 83       | 1030         | USB_MAX_SU07           |

| 24          | 7       | 0       | 0       | 84       | 2054         | USB_RES_SU07           |

| 25          | 8       | 0       | 0       | 82       | 7            | USB_MIN_SU08           |

| 26          | 8       | 0       | 0       | 83       | 1031         | USB_MAX_SU08           |

| 27          | 8       | 0       | 0       | 84       | 2055         | USB_RES_SU08           |

| 28          | 9       | 1       | 1       | 82       | 280          | USB_MIN_MU09_IN1       |

| 29          | 9       | 1       | 1       | 83       | 1304         | USB_MAX_MU09_IN1       |

| 30          | 9       | 1       | 1       | 84       | 2328         | USB_RES_MU09_IN1       |

| 31          | 9       | 2       | 1       | 82       | 296          | USB_MIN_MU09_IN2       |

| 32          | 9       | 2       | 1       | 83       | 1320         | USB_MAX_MU09_IN2       |

| 33          | 9       | 2       | 1       | 84       | 2344         | USB_RES_MU09_IN2       |

The set numbers are computed with:

#### (wIndexH-1) + wValueH\*16 + wValueL\*256

The get number are computed with

=(\$B23-1)+\$C23\*16+(\$E23-82)\*16\*16\*4+\$D23\*16\*16

# wIndexH-1 + wValueH\*16 + bRequest\*256 + (wValueL-82)\*1024

Both set and get numbers are represented with 16bit which is sufficient for this purpose. The other request components are checked by normal "if"-structures.

The flowchart should give a better understandig of this procedure.

- **Note:** The GET\_CUR requests also uses the set\_number table, because the structure of these request is very similiar to the SET\_CUR requests.

- **Note:** The SET\_INDEX is used to identify the request. It the table position where the magic number matches the table entry. In the dsp\_control.asm this index is used as a "jump handler" to the routines which transfer the audio control parameters to the DSP.

#### 5.2.2. Examples

An example will illustrate how a new feature is added.

#### 5.2.2.1. How to add new Features and Requests

We want to add the loudness function as an additional tone control in the audio path. This is already implemented in the DSP and only needs to be activated. In order to do that we need the following steps.

#### How to change the Descriptor

We need to modify the feature unit 1 (FU1) in the following way:

| .ec        | Įu           | FU_ID1        | 1   |                                                              |

|------------|--------------|---------------|-----|--------------------------------------------------------------|

| ;CS-specif | ic Feature U | Init Descript | tor |                                                              |

| .by        | /te          | 0x0d          |     | ;bLength                                                     |

| .by        | /te          | 0x24          |     | ;Audio class specific interface desc                         |

| .by        | /te          | 0x06          |     | ;Feature Unit descriptor                                     |

| AUDIO_F    | EATURE_U     | JNIT_ID1:     |     |                                                              |

| .by        | /te          | FU_ID1        |     | ;Unit ID                                                     |

| .by        | /te          | MU_ID9        |     | ;Source ID                                                   |

| .by        | /te          | IT_ID12       |     | ;Source ID ###KS                                             |

| .by        | /te          | 0x02          |     | ;ControlSize Length in bytes of bmaControls                  |

| .rv        | vord         | 0x0355        |     | ;bmaControls(0);defines supported features in master channel |

| .rv        | vord         | 0x0002        |     | ;bmaControls(1);defines supported features in log. channel 0 |

| .rv        | vord         | 0x0002        |     | ;bmaControls(2);defines supported features in log. channel 1 |

| .by        | /te          | 0x00          |     | ;iFeatureindex of string descriptor, descr. feature unit     |

Loudness works on both channels, so we need to modify the bma Control(0), which lists all feature in the master channel (all features which cannot controlled separetely for left and right channel are listed here). Looking into the audio class spec tells us that loudness is activated by bit9 in the bma-Control(0). So the new bmaControl is:

.rword 0x0355

;bmaControls(0)

#### How to implement the Request Handling

Upon enumeration the host now knows that the device supports loudness, and tries to read the characteristics of this feature. The only parameter of interest here is a boolean variable, that switches loudness on and off. Unlike volume requests or bass/treble request there are no MIN/MAX/RES parameters here. So we only have to extend the SET-table.

We add Request Nr. 18:

| Request Nr. | wInd-<br>exH | wValueH | wValueL | magic number | Request Name  |  |  |

|-------------|--------------|---------|---------|--------------|---------------|--|--|

| 18          | 1            | 10      | 0       | 296          | FU1_LOUDN_CUR |  |  |

...

The magic number according to the formula:

## (wIndexH-1) + wValueH\*16 + wValueL\*256 is then

0 + 10x16 + 0x256 = 160

This number is added at the end of the set-table

...

| .rword | 280 | ; MU9_IN1_CUR   |

|--------|-----|-----------------|

| .rword | 296 | ; MU9_IN2_CUR   |

| .rword | 160 | ; FU1_LOUDN_CUR |

This allows to detect if the host wants to set or get the CUR-value.

| Now  | we   | need  | to  | add     | a    | new      | RAM-variable |  |  |

|------|------|-------|-----|---------|------|----------|--------------|--|--|

| USB_ | FU1_ | LOUDN | CUR | R, whic | h hơ | olds the | CUR-status:  |  |  |

| SB_SU8_CUR:        | .rword | 0x0000 | ;15 |

|--------------------|--------|--------|-----|

| USB_MU9_IN1_CUR:   | .rword | 0x0000 | ;16 |

| USB_MU9_IN2_CUR:   | .rword | 0x0000 | ;17 |

| USB_FU1_LOUDN_CUR: | .rword | 0x0000 | ;18 |

Remember: the set-table and the CUR-table are both located in usb\_audio\_ctl\_include.asm

#### How to implement the DSP-control

From the USB-host point of view everything is ok now: the device reports loudness as an audio feature, the device accepts setting the CUR-value, and the device reports the CUR-value. But there is still one action missing: the V8 needs to switch the loudness function on and off in the DSP.

jeq XDFP\_RECORD\_SELECT;14 dec r0 jeq XDFP\_ANALOG\_VOLUME;15 dec r0 jeq XDFP\_USBDOWN\_VOLUME;16 dec r0 jeq XDFP\_LOUDNESS rts

and then, of course, we need to add the new routine XDFP\_LOUDNESS. The easiest way to do this is to copy and paste an already existing function and change some names

XDFP LOUDNESS:

| .equ   | XDFPADR_PLAYBACK_LOUDN0x15         | ; XDFP-ADDRESS for Loudness                |

|--------|------------------------------------|--------------------------------------------|

| .equ   | XDFP_LOUDNESS0x30                  |                                            |

| ; XDFI | P needs 0x00=Loudness-OFF          | ; 0x30=Loudness-ON                         |

| ; USB  | sends 0=Loudness-OFF 1=Loudness-ON |                                            |

| ldi    | r2, XDFP_LOUDNESS                  | ; this defines the Loudness-Characteristic |

| lda    | r1, USB_FU1_LOUDN_CUR              |                                            |

| brne   | LOUDNON                            |                                            |

| lda    | r2, 0x00                           | ; Loudness off                             |

| LOUD   | NON:                               |                                            |

| ldi    | r1, XDFPADR_PLAYBACK_LOUDN         |                                            |

| jmp    | XDFP_SEND_3BYTES                   | ;sends Loudness,0,0 (Hi,Mi,Lo) with rts    |

|        |                                    |                                            |

|        |                                    |                                            |

Another option here would be to put the XDFP\_LOUDNESS into the Section1 as a parameter that comes from the EEPROM, because the loudness characteristic in the DSP can be set to various modes. Using 0x30 is just one example. See the document UACB – DSP firmware for more info on the loudness. This happens in dsp\_control.asm. This routine is called after the SET-request and uses the RAM-variable SET\_INDEX as branching control to the corresponding DSP-control-routines. The SET\_INDEX is the SET-table position of the detected request, i.e. 18 for our new request.

We extend the branch structure in dsp\_control.asm

#### Initialisation

The DSP sets all variables to zero after power up. This means for our example that loudness is off. This, however has to correlate with the CUR-value in the V8. Without any

... ;

init the Audio\_Class

ldi r0,0x80sta r0, USB\_FU1\_VOL\_CH1\_CUR;mute the playback volumesta r0, USB\_FU1\_VOL\_CH2\_CUR;mute the playback volumeldi r0, 0x01;mute the playback volumesta r0, USB\_SU7\_CUR;init the SU7 to Mic-Inputxor r0sta r0, USB FU1 LOUDN CUR

Now everything is ready to switch Loudness on and off under control of the operating system. Unfortunately the WIN mixer does not provide any controls to do that, so this feature was not implemented in the standard firmware.

Fig. 5–3:

initialisation the CUR-values are all set to zero after power up and this is exactly what we need. But it is recommended to always do the initialisation. This is done in the main include.asm.

# 5.3. DSP Control

The code in dsp\_control.asm handles the communication between the V8 and the DSP. In the standard firmware its is a one-way communication, which means, data are sent to from the V8 to the DSP, but nothing is read back. Other applications, however, may require this, and therefore the hardware is prepared to do that.

This hardware is highlighted first because it is essential for understanding this communication.

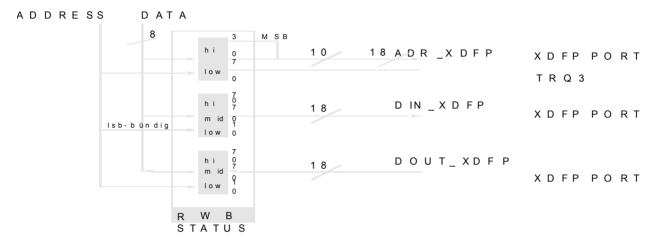

The next figure shows the control interface between V8 and DSP:

### Fig. 5–4:

The DSP-RAM has a wordlength of 18-bit and so we need 3-bytes from the V8 to completely write one DSP-location. So we have 3-bytes both for each direction. In case of writing into the DSP these bytes are named:

- XDFP\_DATAIN\_HI

- XDFP\_DATAIN\_MI

- XDFP\_DATAIN\_LO

and this bytes represent one DSP word as follows:

| XDFP_DAT<br>AIN_ | HI-7 | HI-6 | HI-5 | HI-4 | HI-3 | HI-2 | HI-1 | HI-0 | MI-7 | MI-6 | MI-5 | MI-4 | MI-3 | MI-2 | MI-1 | MI-0 | LO-1 | LO-0 |

|------------------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|

| DSP-word         | 17   | 16   | 15   | 14   | 13   | 12   | 11   | 10   | 9    | 8    | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

The address space of the DSP is 10-bit, so we need 2-bytes to address this. This bytes are named:

- XDFP\_ADR\_HI

- XDFP\_ADR\_LO

and build the DSP\_address plus R/W -control as follows:

| XDFP_ADRHI7 _   | _HI6 _HI5 | _HI4 | _HI3 | _HI2          | _HI1 | _HI0 | _LO7 | _LO6 | _LO5 | _LO4 | _LO3 | _LO2 | _LO1 | _LO0 |

|-----------------|-----------|------|------|---------------|------|------|------|------|------|------|------|------|------|------|

| DSP_<br>ADDRESS |           |      |      | 0= RD<br>1=WR | 9    | 8    | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

The Read, Write, Busy status-bits are needed as handshake signals. Their meaning will become clear after the description of the write and read sequence below:

#### Write Sequence:

V8 has to transmit:

- XDFP\_DATAIN\_LO

- XDFP\_DATAIN\_MI

- XDFP\_DATAIN\_HI

- XDFP\_ADR\_HI

- XDFP\_ADR\_LO

The transmission of the low-addressbyte generates the write-interrupt for the DSP and sets the W- and B-bit in the statusregister.

The W- and the B-Bit are reset, when the DSP reads the indata-register

The W-bit is redundant here and is not used in the standard firmware

#### **Read Sequence**

V8 has to transmit:

- XDFP\_ADR\_HI

- XDFP\_ADR\_LO

The transmission of the low-addressbyte generates the readinterrupt for the XDFP and sets the R- and the B-bit. The DSP reads the address and writes the required data word into the out-data register This resets the R-bit.

V8 has to poll the R-bit and fetch the 3-bytes after the R-bit is reset:

- XDFP\_DATAOUT\_HI

- XDFP\_DATAOUT\_MI

- XDFP\_DATAOUT\_LO

The B-bit is reset after the LO-data is fetched from the V8.

The write-sequence is already implemented in the standard firmware and there should be no need to change this. The routine is located in the upper-rom and is called **XDFP\_SEND\_3bytes**. This routine handles the complete write sequence, including the handshake (using B-bit).

The values are passed by registers:

- $r1 = XDFP_ADR_LO$

- $r2 = XDFP_DATAIN_HI$

- $r3 = XDFP_DATAIN_MI$

- $r4 = XDFP_DATAIN_LO$

There is no XDFP\_ADR\_HI and so only the lower 256 words within the DSP-RAM-space can be addressed with this routine. The DSP-firmware, however, holds all control variables within this lower address space, so there is no need for the HI-byte.

In the same way a **XDFP\_READ\_3bytes** can be created.

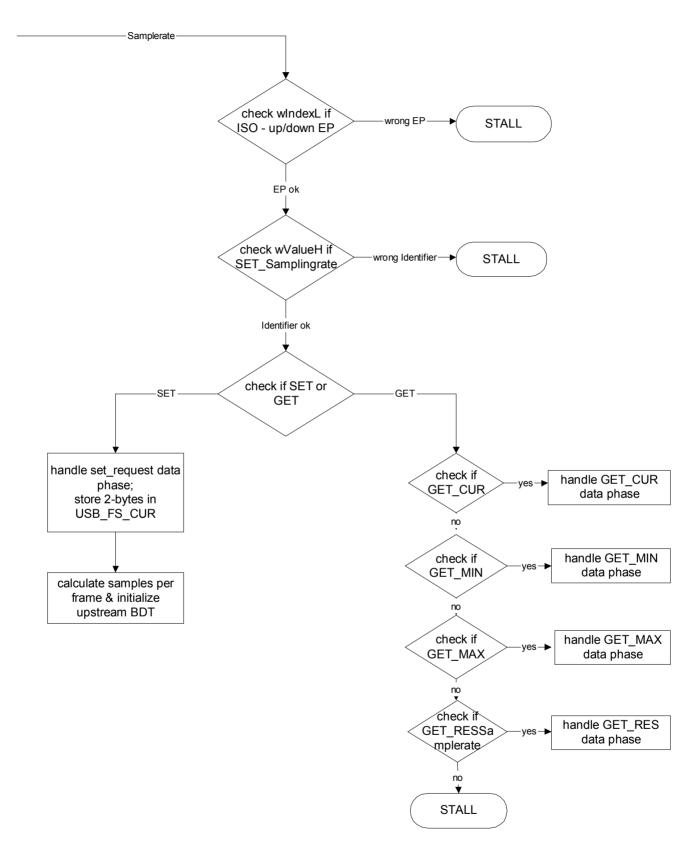

#### 5.4. Sample Rate Control

The samplerate requests are endpoint control requests and are needed for ISO upstreaming. The SET\_SAMPLERATE tells the device how many audio samples per frame the host expects. The samplerate is represented as a 3-byte word, but for the UACB samplerate range (6.4kHz ...48kHz) only 2-bytes are required, so the high byte is ignored for further processing.

The samplingrate is specified in Hz. So 0x00bb80 is transferred with the SET\_SAMPLERATE request, when 48000Hz is required. This number is the input for an algorithm that computes the number of samples per frame, i.e. samples per millisecond, what is basically a "devide by 1000" operation in case of "integer multiples of 1000" samplerates. In all other cases the "devide by 1000" algorithm result in a nonzero remainder. This remainder is then accumulated 1000 times and when the accumulator overflows an additional sample is transmitted.

The samplerate goes into the DSP too. Here it is needed as an initial value for the samplerate conversion.

- **Note:** The A/D conversion is running on 48kHz, independantly of what the iso-upstream requires. The adaption to the required samplerate is done by samplerate conversion.

- **Note:** It is observed that SET\_SAMPLERATE is also transferred preceeding an iso-downstream. This was not the case with downstream-only devices (UACA). Here this information is not required but on the other hand it is not allowed to stall this request. So it is handled also. Otherwise the host would never send iso-downstream data.

The following samplingrate request are supported:

- SET CUR

- GET CUR

- GET MIN

- GET MAX

- GET RES

After a SET CUR request the samples per frame are calculated and stored in the upstream BDT.

At this point the complete algorithm is running including the "devide by 1000" code ("subtract 1000 until result is negative").

During ISO-uopstream only the fractional part of the "samples per frame" algorithm is computed. The integer part does not change at a given samplerate.

Fig. 5–5: Sample rate control handling

#### 6. GPIO Handling

This chapter describes the usage of the 12 GPIO pins. First a description of the various modes is given.

Each GPIO-pin can be used either as input or as output pin. The direction of each pin is defined in the following hard-ware control registers:

\_LO defines GPIO0....7LSB == GPIO0, MSB == GPIO7

\_HI defines GPIO8..11LSB == GPIO8; BIT3 == GPIO11

GPIO\_CONFIG\_LO0xb0510 = input; 1 = output GPIO\_CONFIG\_HI0xb058

In case of output, the padstrength (value???) can be set to either high or low: (for other pins see the UACB – V8 reference)

GPIO PADSTRENGTH LO:0xb0550 = weak; 1 = strong

GPIO\_PADSTRENGTH\_HI:0xb056

In case of input, an internal pulldown (250k) can be switched either on and off

GPIO\_PULLDOWN\_LO0xb0590 = pulld. on; 1 = pulld. off GPIO\_PULLDOWN\_HI0xb05a

The standard firmware defines the default GPIO characteristic in Section1:

SED\_DEFAULT\_GPIO\_CONFIG\_LO\_DEFAULT:; default 0, 1 = output

.byte 0x00

SED\_DEFAULT\_GPIO\_CONFIG\_HI\_DEFAULT:; default 0, 1 = output

.byte 0x00

SED\_DEFAULT\_GPIO\_PULLDOWN\_LO\_DEFAULT:; default: 1 (pulldown on) .byte 0xff

```

SED_DEFAULT_GPIO_PULLDOWN_HI_DEFAULT:; default: 1 (pulldown on)

.byte 0xff

```

SED\_DEFAULT\_GPIO\_PADSTRENGTH\_LO\_DEFAULT:; default: 0 (weak) .byte 0x00

SED\_DEFAULT\_GPIO\_PADSTRENGTH\_HI\_DEFAULT:; default: 0 (weak) .byte 0x00

This values are copied from the bootloader into the Section1 RAM mirror image (see Section1 concept) and from there copied into RAM shadow registers. This was required because the hardware control register are read only and so the V8 needs to keep track of the actual status either for internal purpose or for reporting it to an external controller (USB-Host, I2C-Controller etc). This is used for some other hardware register too. Unfortunately this wastes some RAM space The following sequence (including the RAM addresses) can be found in main\_include.asm:

- A709 lda r0, GPIO\_CONFIG\_LO\_DEFAULT

- A184 sta r0, GPIO\_CONFIG\_LO\_SHADOW

- A70A lda r0, GPIO\_CONFIG\_HI\_DEFAULT

- A185 sta r0, GPIO\_CONFIG\_HI\_SHADOW

- A70B lda r0, GPIO\_PULLDOWN\_LO\_DEFAULT

- A186 sta r0, GPIO\_PULLDOWN\_LO\_SHADOW

- A70C lda r0, GPIO\_PULLDOWN\_HI\_DEFAULT

- A187 sta r0, GPIO\_PULLDOWN\_HI\_SHADOW

- A70D lda r0, GPIO\_PADSTRENGTH\_LO\_DEFAULT

- A188 sta r0, GPIO\_PADSTRENGTH\_LO\_SHADOW

- A70E lda r0, GPIO\_PADSTRENGTH\_HI\_DEFAULT

- A189 sta r0, GPIO\_PADSTRENGTH\_HI\_SHADOW

The shadow registers are then copied into the hardware register in the routine V8\_RESTORE\_SHADOW\_REGS (also located in main\_include.asm). The routine V8\_RESTORE\_SHADOW\_REGS runs after RESET and is also called in the scheduler taks 5 (see "The Scheduler Concept"). By setting the associated scheduler bit the routine runs every 1ms.

This automatic update allows to control the GPIOs just by setting the shadow registers. In this case, however, it must be observed that there may be a delay of up to 1ms between writing into the shadow registers and the update of the hardware register. If this delay is not acceptable, the hardware

The status of the lower bits 0...7 is defined in: b0A0GPO REG[0:7]

The status of the upper bits 8...11 is defined in:

b0A1GPIO\_REG[4...7]

The status of the lower input pins 0...7 is found in: b0A2GPI\_REG[0...7]

The status of the upper input pins 8...11 is found in b0A1GPIO\_REG[0...3]

Here we don't need the shadow register concept, because all this register are readable.

**Note:** The standard firmware uses only GPIO0..3 as input pins for the HID functions.

registers needs to be controlled directly. In this case, however, it is strictly recommended to update the shadow registers too, in order to have identical information in both hardware and shadow registers.

In most applications the configuration of the GPIOs will be static, i.e: a pin is either input or output, with or without pulldown etc., and this configuration is defined in section1 as default data.

More important for applications, however, is the writing or reading to or from the GPIO pins itself.

#### 6.1. Memory Mapped Mode

The GPIOs can also be used in a memory mapped mode. This means the address range

b0b0...b0bf

How does the standard firmware use the GPIOs?

Looking into the report descriptor tells that four HID audio control functions are defined:

; assigned real keys

| .rword | 0xE909 | ; Usage Volume UP   |

|--------|--------|---------------------|

| .rword | 0xEA09 | ; Usage Volume DOWN |

| .rword | 0xE209 | ; Usage MUTE        |

| .rword | 0xE509 | ; Usage BASS BOOST  |

This functions are assigned to the GPIO0...3. High level at GPIO0 ramps up the volume for example.

This means this pins need to be polled by the V8, in order to report their state on request to the host.

#### 6.2. Debouncing

For debouncing a simple timer function is used. After detection of high level at one of the GPIO..3 a timer (KEY\_TIMER) is started (software timer) counting from MAX\_KEY\_TIMER down to zero. MAX\_KEY\_TIMER is defined in Section1

SED\_DEFAULT\_MAX\_KEY\_TIMER:

.byte 0x7f

As long as the counter did not finish zero, there is no new polling. This timer also defines the repetition rate of a permanent pressed key (defines for example, how fast the volume slider in the WIN mixer goes up and down).

**Note:** This simple method does not protect from noise or spikes on the pins. For this kind of problems averaging algorithm should be used.

the addressbus. This means for example, writing a 0xaa to b0bf results in 0xaa at the GPIO0...7 and 0xf at GPIO8...11. In this mode the GPIO8...11 need to be set as output pins, of course.

is transparent to the GPIOs. GPIO0..7 are mapped to the

databus and GPIO8...11 are mapped to the lower four bits of

As polling rate the 1ms timebase is used, which is provided in the scheduler. Scheduler task 0 calls the routine USB\_GET\_KEY located in gpio\_control.asm. Some notes on the USB\_GET\_KEY is given below.

#### 6.3. Reporting the Keycode